# **DPA423-426**

# **DPA-Switch®** Family

# Highly Integrated DC-DC Converter ICs for Power over Ethernet & Telecom DC-DC

# **Product Highlights**

### **Highly Integrated Solution**

- Eliminates 20-50 external components—saves space, cost

- Integrates 220 V high frequency MOSFET, PWM control

- Lower cost plastic DIP surface mount (G package) and through-hole (P package) options for designs ≤35 W

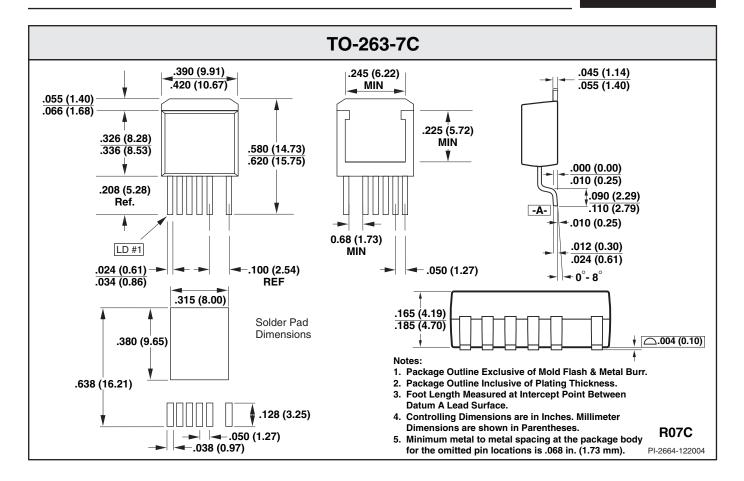

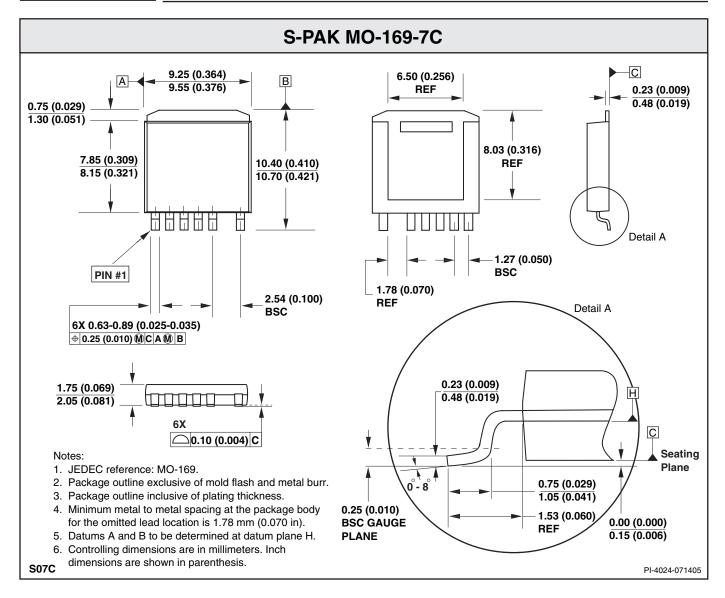

- Thermally efficient MO-169-7C (S-PAK) and TO-263-7C (R package) options for high power applications

## **Superior Performance and Flexibility**

- Eliminates all external current sensing circuitry

- Built-in auto-restart for output overload/open loop protection

- Pin selectable 300/400 kHz fixed frequency

- Wide input (line) voltage range: 16-75 VDC

- Externally programmable current limit

- Source connected tab reduces EMI

- Line under-voltage (UV) detection: meets ETSI standards

- Line overvoltage (OV) shutdown protection

- UV/OV limits gate drive voltage for synchronous rectification

- Fully integrated soft-start for minimum stress/overshoot

- Supports forward or flyback topology

- Cycle skipping: regulation to zero load without pre-load

- · Hysteretic thermal shutdown for automatic fault recovery

- RoHS compliant P, G and S package options

# **EcoSmart**® - Energy Efficient

- · Extremely low consumption at no load

- Cycle skipping at light load for high standby efficiency

## **Applications**

- · PoE applications, VoIP phones, WLAN, security cameras

- Telco central office equipment: xDSL, ISDN, PABX

- Distributed power architectures (24 V/48 V bus)

- Industrial controls

# **Description**

The *DPA-Switch* IC family is a highly integrated solution for DC-DC conversion applications for 16-75 VDC input.

DPA-Switch uses the same proven topology as TOPSwitch, cost effectively integrating a power MOSFET, PWM control, fault protection and other control circuitry onto a single CMOS chip. High performance features are enabled with three user configurable pins. Hysteretic thermal shutdown is also provided. In addition, all critical

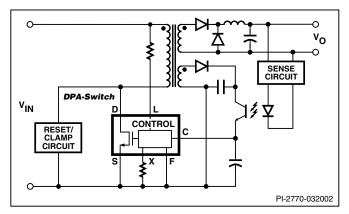

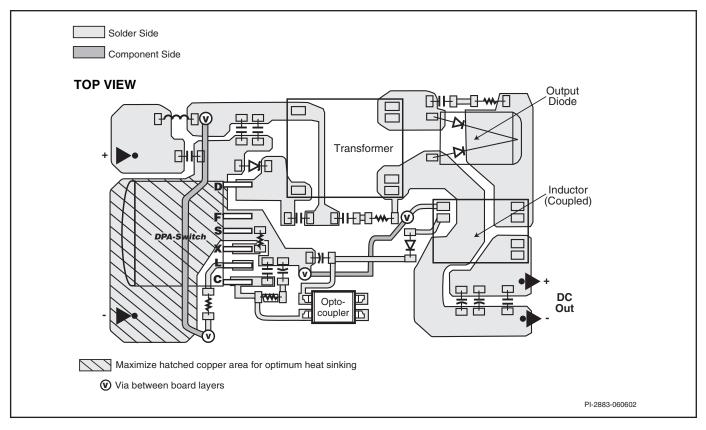

Figure 1. Typical Forward Converter Application.

| 0                                            | UTPL       | JT PC  | W   | ΕF  | R TA       | BLE      |                     |  |  |

|----------------------------------------------|------------|--------|-----|-----|------------|----------|---------------------|--|--|

| 36-75 VDC INPUT RANGE (FORWARD) <sup>2</sup> |            |        |     |     |            |          |                     |  |  |

| Total Device Dissipation <sup>3</sup>        | 0.5 W      | 1 W    | 2.5 | W   | 4 W        | 6 W      | Max<br>Power        |  |  |

| PRODUCT <sup>4</sup>                         |            |        |     |     |            |          | Output <sup>1</sup> |  |  |

| DPA423                                       | 12 W       | 16 W   | -   |     | -          | -        | 18 W                |  |  |

| DPA424                                       | 16 W       | 23 W   | 35  | W   | -          | -        | 35 W                |  |  |

| DPA425                                       | 23 W       | 32 W   | 50  | W   | 62 V       | <b>V</b> | 70 W                |  |  |

| DPA426⁵                                      | 25 W       | 35 W   | 55  | W   | 70 V       | V 83 W   | 100 W               |  |  |

| 36-75                                        | VDC IN     | IPUT I | RAN | 1G  | E (FL      | YBACK    | <b>)</b> ²          |  |  |

| Total Device<br>Dissipation <sup>3</sup>     | 0.5 W      | 0.75   | w   | 1 W |            | 1.5 W    | Max<br>Power        |  |  |

| PRODUCT <sup>4</sup>                         |            |        |     |     |            |          | Output <sup>1</sup> |  |  |

| DPA423                                       | 9 W        | 13     | w   |     | -          | -        | 13 W                |  |  |

| DPA424                                       | 10 W       | 14.5   | W   | 18  | 8 W        | 24 W     | 26 W                |  |  |

| DPA425                                       | <b>_</b> 6 | _6     |     |     | <b>_</b> 6 | 25.5 W   | 52 W                |  |  |

Table 1. Notes: 1. Maximum output power is limited by device internal current limit. 2. See Applications Considerations section for complete description of assumptions and for output powers with other input voltage ranges. 3. For device dissipation of 1.5 W or below, use P or G packages. Device dissipation above 1.5 W is possible with S and R packages. 4. Packages: P: DIP-8, G: SMD-8, R: TO-263-7C, S: MO-169-7C. For lead-free package options, see Part Ordering Information. 5. Available in S and R package only. 6. Due to higher switching losses, the DPA425 may not deliver additional power compared to a smaller device.

parameters (i.e. current limit, frequency, PWM gain) have tight temperature and absolute tolerance, to simplify design and reduce system cost.

# Section List

| Functional Block Diagram                                           | ও  |

|--------------------------------------------------------------------|----|

| Pin Functional Description                                         | 3  |

| DPA-Switch Family Functional Description                           | 4  |

| CONTROL (C) Pin Operation                                          |    |

| Oscillator and Switching Frequency                                 |    |

| Pulse Width Modulator & Maximum Duty Cycle                         | 6  |

| Minimum Duty Cycle and Cycle Skipping                              | 6  |

| Error Amplifier                                                    | 6  |

| On-chip Current Limit with External Programmability                | 6  |

| Line Under-Voltage Detection (UV)                                  | 6  |

| Line Overvoltage Shutdown (OV)                                     |    |

| Line Feed-Forward with DC <sub>MAX</sub> Reduction                 |    |

| Remote ON/OFF                                                      |    |

| Synchronization                                                    |    |

| Soft-Start                                                         |    |

| Shutdown/Auto-Restart                                              |    |

| Hysteretic Over-Temperature Protection                             |    |

| Bandgap Reference                                                  |    |

| High-Voltage Bias Current Source                                   |    |

| Using Feature Pins                                                 |    |

| FREQUENCY (F) Pin Operation                                        |    |

| LINE-SENSE (L) Pin Operation                                       |    |

| EXTERNAL CURRENT LIMIT (X) Pin Operation                           |    |

| Typical Uses of FREQUENCY (F) Pin                                  |    |

| Typical Uses of LINE-SENSE (L) and EXTERNAL CURRENT LIMIT (X) Pins | 12 |

| Application Examples                                               | 15 |

| Key Application Considerations                                     | 18 |

| DPA-Switch Design Considerations                                   |    |

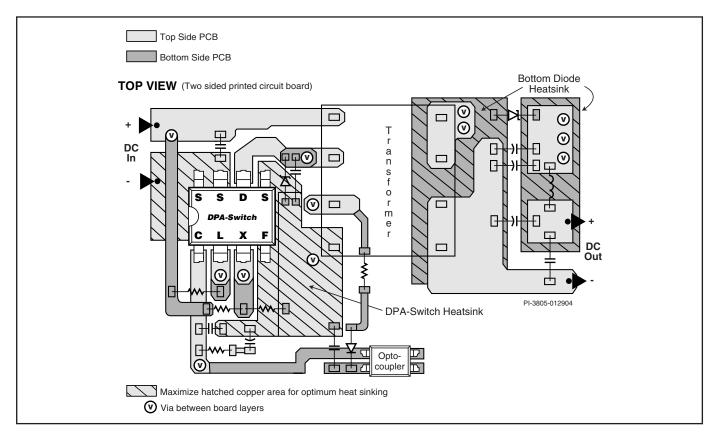

| DPA-Switch Layout Considerations                                   | 19 |

| Quick Design Checklist                                             | 20 |

| Design Tools                                                       | 20 |

| Product Specifications and Test Conditions                         | 22 |

| Typical Performance Characteristics                                | 28 |

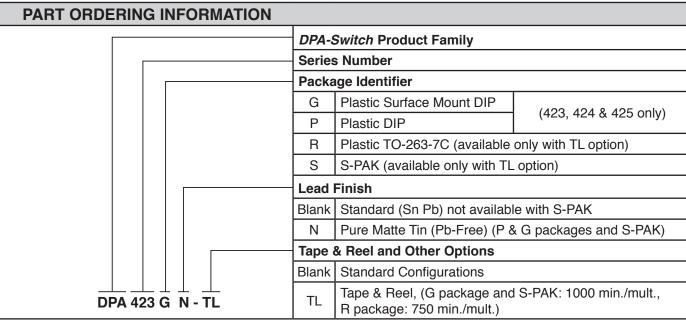

| Part Ordering Information                                          |    |

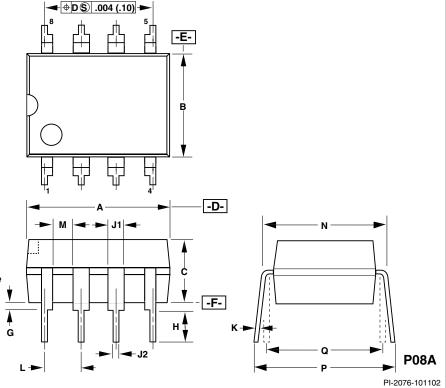

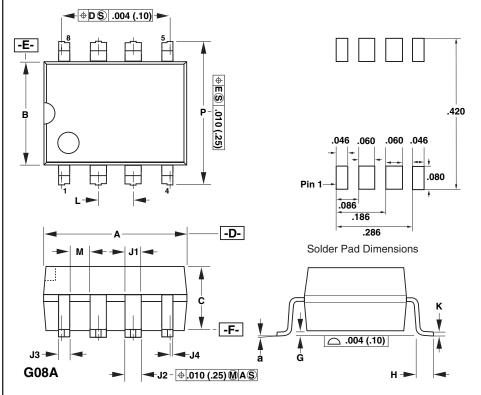

| Package Outlines                                                   |    |

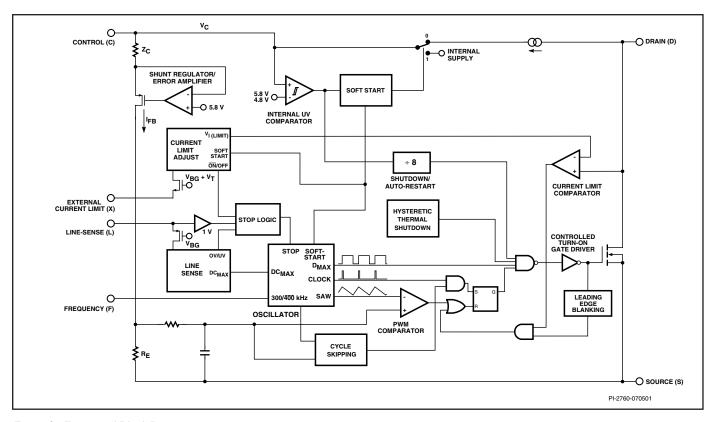

Figure 2. Functional Block Diagram.

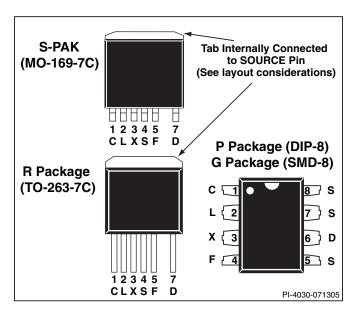

# **Pin Functional Description**

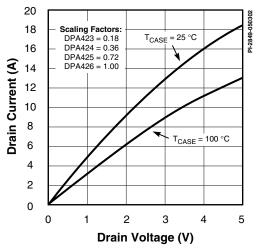

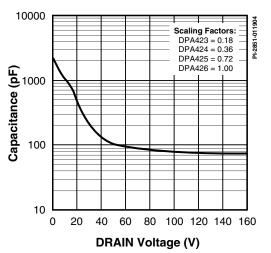

#### DRAIN (D) Pin:

High voltage power MOSFET drain output. The internal startup bias current is drawn from this pin through a switched high-voltage current source. Internal current limit sense point for drain current.

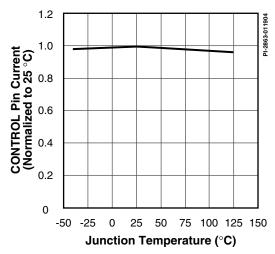

## **CONTROL** (C) **Pin:**

Error amplifier and feedback current input pin for duty cycle control. Internal shunt regulator connection to provide internal bias current during normal operation. It is also used as the connection point for the supply bypass and auto-restart/compensation capacitor.

## LINE-SENSE (L) Pin:

Input pin for overvoltage (OV), under-voltage (UV) lock out, line feed-forward with the maximum duty cycle ( $DC_{MAX}$ ) reduction, remote ON/OFF and synchronization. A connection to SOURCE pin disables all functions on this pin.

#### **EXTERNAL CURRENT LIMIT (X) Pin:**

Input pin for external current limit adjustment and remote ON/OFF. A connection to SOURCE pin disables all functions on this pin.

#### **FREQUENCY (F) Pin:**

Input pin for selecting switching frequency: 400 kHz if

connected to SOURCE pin and 300 kHz if connected to CONTROL pin.  $\,$

### **SOURCE (S) Pin:**

Output MOSFET source connection for the power return. Primary side control circuit common and reference point.

Figure 3. Pin Configuration (top view).

# **DPA-Switch** Family Functional Description

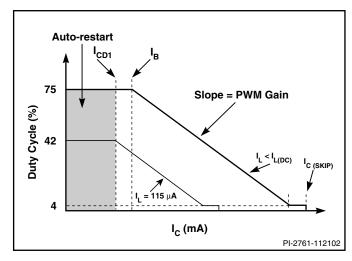

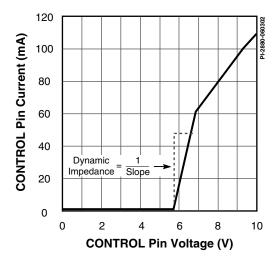

*DPA-Switch* is an integrated switched mode power supply chip that converts a current at the control input to a duty cycle at the open drain output of a high voltage power MOSFET. During normal operation the duty cycle of the power MOSFET decreases linearly with increasing CONTROL pin current as shown in Figure 4. A patented high-voltage CMOS technology allows both the high-voltage power MOSFET and all the low voltage control circuitry to be cost effectively integrated onto a single monolithic chip.

In addition to the standard *TOPSwitch* features, such as the high-voltage start-up, the cycle-by-cycle current limiting, loop compensation circuitry, auto-restart and thermal shutdown, *DPA-Switch* also offers many advanced features that reduce system cost and increase power supply performance and design flexibility. Following is a summary of the advanced features:

- A fully integrated 5 ms soft-start limits peak currents and voltages during start-up and reduces or eliminates output overshoot in most applications.

- 2. A 75% maximum duty cycle (DC<sub>MAX</sub>) together with the line feed-forward with DC<sub>MAX</sub> reduction feature makes *DPA-Switch* well suited for both flyback and forward topologies.

- 3. High switching frequency (400 kHz/300 kHz, pin selectable) allows the use of smaller size transformers and offers high bandwidth for power supply control loop.

- 4. Cycle skipping operation at light load minimizes standby power consumption (typically <10 mA input current).

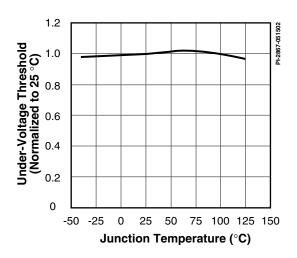

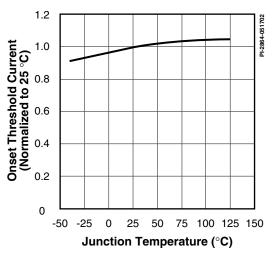

- Line under-voltage ensures glitch free operations at both power-up and power-down and is tightly toleranced over process and temperature to meet system level requirements common in DC to DC converters (e.g. ETSI).

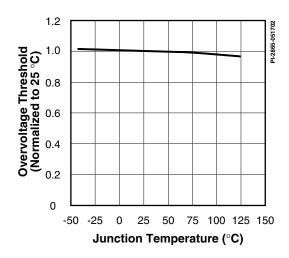

- 6. Line overvoltage protects *DPA-Switch* against excessive input voltage and line surge.

- 7. External current limit adjustment allows the setting of the current limit externally to a lower level near the operating peak current and, if desired, further adjusts the level gradually as line voltage rises. This makes possible an ideal implementation of overload power limiting.

- 8. Synchronization function allows the synchronization of *DPA-Switch* operation to an external lower frequency.

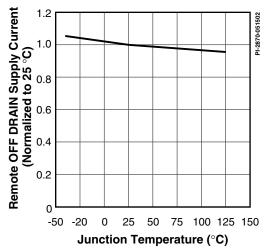

- Remote ON/OFF feature permits DPA-Switch based power supplies to be easily switched on/off using logic signals. Maximum input current consumption is 2 mA in remote OFF.

- Hysteretic over-temperature shutdown provides automatic recovery from thermal fault.

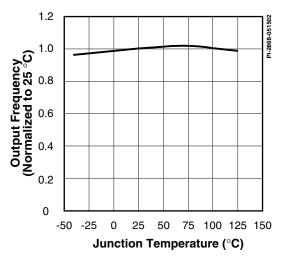

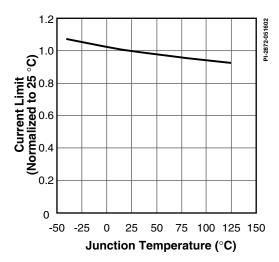

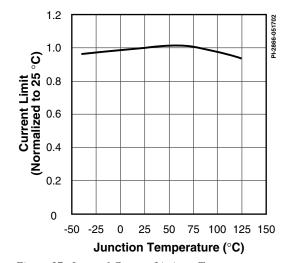

- Tight absolute tolerances and small temperature variations on switching frequency, current limit, and under-voltage lock out threshold (UV).

Figure 4. Relationship of Duty Cycle to CONTROL Pin Current.

Three pins, LINE-SENSE (L), EXTERNAL CURRENT LIMIT (X) and FREQUENCY (F), are used to implement all the pin controllable features. A resistor from the LINE-SENSE pin to DC input bus implements line UV, line OV and line feed-forward with  $DC_{MAX}$  reduction. A resistor from the EXTERNAL CURRENT LIMIT pin to the SOURCE pin sets current limit externally. In addition, remote ON/OFF may be implemented through either the LINE-SENSE pin or the EXTERNAL CURRENT LIMIT pin depending on the polarity of the logic signal available as well as other system specific considerations. Shorting both the LINE-SENSE and the EXTERNAL CURRENT LIMIT pins to the SOURCE pin disables line OV, line UV, line feed-forward with DC<sub>MAX</sub> reduction, external current limit, remote ON/OFF and synchronization. The FREQUENCY pin sets the switching frequency to 400 kHz if connected to the SOURCE pin, or 300 kHz if connected to the CONTROL pin. This pin should not be left open. Please refer to "Using Feature Pins" section for detailed information regarding the proper use of those pins.

#### **CONTROL (C) Pin Operation**

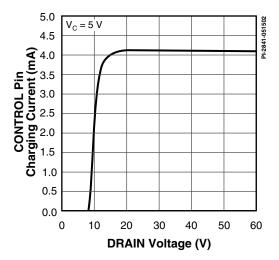

The CONTROL pin is a low impedance node that is capable of receiving a combined supply and feedback current. During normal operation, a shunt regulator is used to separate the feedback signal from the supply current. CONTROL pin voltage  $V_c$  is the supply voltage for the control circuitry including the MOSFET gate driver. An external bypass capacitor closely connected between the CONTROL and SOURCE pins is required to supply the instantaneous gate drive current. The total amount of capacitance connected to this pin also sets the auto-restart timing as well as control loop compensation.

When the DC input voltage is applied to the DRAIN pin during start-up, the MOSFET is initially off, and the CONTROL pin capacitor is charged through the switched high voltage current source connected internally between the DRAIN and CONTROL pins. When the CONTROL pin voltage V<sub>C</sub> reaches

approximately 5.8 V, the control circuitry is activated and the soft-start begins. The soft-start circuit gradually increases the duty cycle of the MOSFET from zero to the maximum value over approximately 5 ms. The high voltage current source is turned off at the end of the soft-start. If no external feedback/supply current is fed into the CONTROL pin by the end of the soft-start, the CONTROL pin will start discharging in response to the supply current drawn by the control circuitry and the gate current of the switching MOSFET driver. If the power supply is designed properly, and no fault condition such as open loop or overloaded output exists, the feedback loop will close, providing external CONTROL pin current, before the CONTROL pin voltage has had a chance to discharge to the lower threshold voltage of approximately 4.8 V (internal supply under-voltage lockout threshold). When the externally fed current charges the CONTROL pin to the shunt regulator voltage of 5.8 V, current in excess of the consumption of the chip is shunted to SOURCE through resistor  $R_{\scriptscriptstyle\rm E}$  as shown in Figure 2. This current flowing through R<sub>E</sub> controls the duty cycle of the power MOSFET to provide closed loop regulation. The shunt regulator has a finite low output impedance Z<sub>C</sub> that sets the gain of the error amplifier when used in a primary feedback configuration. The dynamic impedance Z<sub>C</sub> of the CONTROL pin together with the external CONTROL pin capacitance sets the dominant pole for the control loop.

When a fault condition such as an open loop or overloaded output prevents the flow of an external current into the CONTROL pin, the capacitor on the CONTROL pin discharges towards 4.8 V. At 4.8 V auto-restart is activated which turns the output MOSFET off and puts the control circuitry in a low current

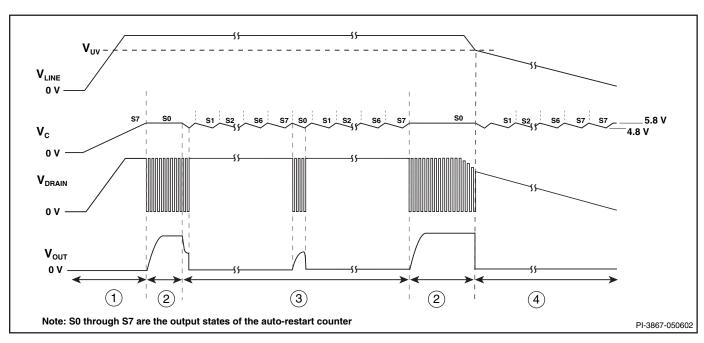

standby mode. The high-voltage current source turns on and charges the external capacitance again. A hysteretic internal supply under-voltage comparator keeps V<sub>C</sub> within a window of typically 4.8 V to 5.8 V by turning the high-voltage current source on and off as shown in Figure 5. The auto-restart circuit has a divide-by-8 counter that prevents the output MOSFET from turning on again until eight discharge/charge cycles have elapsed. This is accomplished by enabling the output MOSFET only when the divide-by-8 counter reaches full count (S7). The counter effectively limits *DPA-Switch* power dissipation as well as the maximum power delivered to the power supply output by reducing the auto-restart duty cycle to typically 4%. Auto-restart mode continues until output voltage regulation is again achieved through closure of the feedback loop.

#### Oscillator and Switching Frequency

The internal oscillator linearly charges and discharges an internal capacitance between two voltage levels to create a sawtooth waveform for the pulse width modulator. The oscillator sets both the pulse width modulator latch and the current limit latch at the beginning of each cycle.

The nominal switching frequency of 400 kHz was chosen to minimize the transformer size and to allow faster power supply loop response. The FREQUENCY pin, when shorted to the CONTROL pin, lowers the switching frequency to 300 kHz, which may be preferable in some applications such as those employing secondary synchronous rectification. Otherwise, the FREQUENCY pin should be connected to the SOURCE pin for the default 400 kHz.

Figure 5. Typical Waveforms for (1) Power Up (2) Normal Operation (3) Auto-restart (4) Power Down.

#### **Pulse Width Modulator and Maximum Duty Cycle**

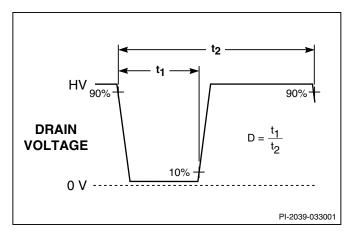

The pulse width modulator implements voltage mode control by driving the output MOSFET with a duty cycle inversely proportional to the current into the CONTROL pin that is in excess of the internal supply current of the chip (see Figure 4). The excess current is the feedback error signal that appears across  $R_{_{\rm F}}$  (see Figure 2). This signal is filtered by an RC network with a typical corner frequency of 30 kHz to reduce the effect of switching noise in the chip supply current generated by the MOSFET gate driver. The filtered error signal is compared with the internal oscillator sawtooth waveform to generate the duty cycle waveform. As the control current increases, the duty cycle decreases. A clock signal from the oscillator sets a latch that turns on the output MOSFET. The pulse width modulator resets the latch, turning off the output MOSFET. Note that a minimum current must be driven into the CONTROL pin before the duty cycle begins to change.

The maximum duty cycle,  $DC_{MAX}$  is set at a default maximum value of 75% (typical). However, by connecting the LINE-SENSE to the DC input bus through a resistor with appropriate value, the maximum duty cycle can be made to decrease from 75% to 33% (typical) as shown in Figure 7 when input line voltage increases (see Line Feed-Forward with  $DC_{MAX}$  Reduction).

#### Minimum Duty Cycle and Cycle Skipping

To maintain power supply output regulation, the pulse width modulator reduces duty cycle as the load at the power supply output decreases. This reduction in duty cycle is proportional to the current flowing into the CONTROL pin. As the CONTROL pin current increases, the duty cycle reduces linearly towards a minimum value specified as minimum duty cycle,  $DC_{MIN}$ . After reaching DC<sub>MIN</sub>, if CONTROL pin current is increased further by approximately 2 mA, the pulse width modulator will force the duty cycle from  $\mathrm{DC}_{\mathrm{MIN}}$  to zero in a discrete step (refer to Figure 4). This feature allows a power supply to operate in a cycle skipping mode when the load consumes less power than the DPA-Switch delivers at minimum duty cycle, DC<sub>MIN</sub>. No additional control is needed for the transition between normal operation and cycle skipping. As the load increases or decreases, the power supply automatically switches between normal and cycle skipping mode as necessary.

Cycle skipping may be avoided, if so desired, by connecting a minimum load at the power supply output such that the duty cycle remains at a level higher than  $DC_{MIN}$  at all times.

#### **Error Amplifier**

The shunt regulator can also perform the function of an error amplifier in primary side feedback applications. The shunt regulator voltage is accurately derived from a temperature-compensated bandgap reference. The gain of the error amplifier is set by the CONTROL pin dynamic impedance. The CONTROL pin clamps external circuit signals to the  $\rm V_{\rm C}$  voltage level.

The CONTROL pin current in excess of the supply current is separated by the shunt regulator and flows through  $R_{\rm E}$  as a voltage error signal.

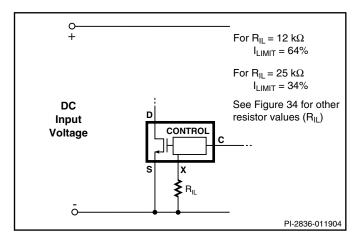

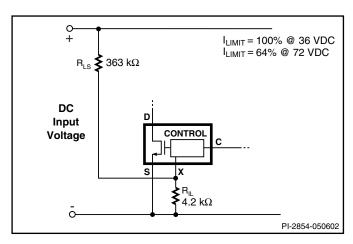

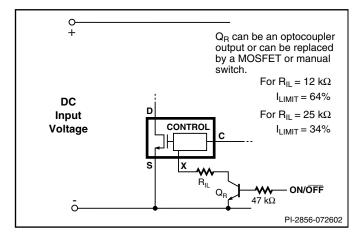

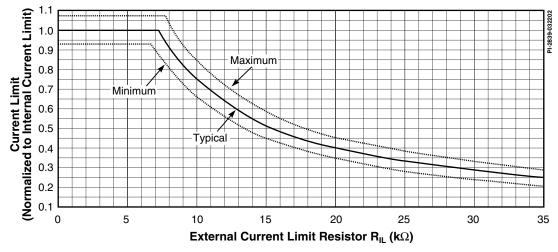

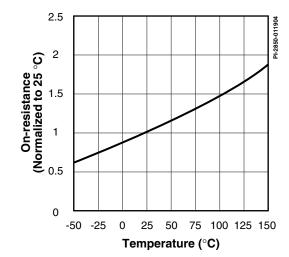

#### **On-chip Current Limit with External Programmability**

The cycle-by-cycle peak drain current limit circuit uses the output MOSFET ON-resistance as a sense resistor. A current limit comparator compares the output MOSFET on-state drain to source voltage,  $V_{DS(ON)}$  with a threshold voltage. At the current limit,  $V_{DS(ON)}$  exceeds the threshold voltage and the MOSFET is turned off until the start of the next clock cycle. The current limit comparator threshold voltage is temperature compensated to minimize the variation of the current limit due to temperature related changes in  $R_{\rm DS(ON)}$  of the output MOSFET. The default current limit of *DPA-Switch* is preset internally. However, with a resistor connected between EXTERNAL CURRENT LIMIT pin and SOURCE pin, the current limit can be programmed externally to a lower level between 25% and 100% of the default current limit. Please refer to the graphs in the Typical Performance Characteristics section for the selection of the resistor value. By setting current limit low, a larger DPA-Switch than necessary for the power required can be used to take advantage of the lower R<sub>DS(ON)</sub> for higher efficiency/smaller heat sinking requirements. With a second resistor connected between the EXTERNAL CURRENT LIMIT pin and the DC input bus, the current limit is reduced with increasing line voltage, allowing a true power limiting operation against line variation to be implemented in a flyback configuration.

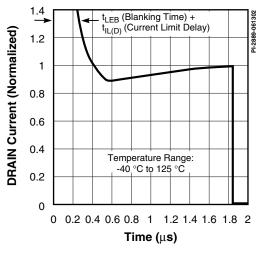

The leading edge blanking circuit inhibits the current limit comparator for a short time after the output MOSFET is turned on. The leading edge blanking time has been set so that, if a power supply is designed properly, current spikes caused by primary-side capacitance and secondary-side rectifier reverse recovery time should not cause premature termination of the switching pulse.

The current limit after the leading edge blanking time is as shown in Figure 31. To avoid triggering the current limit in normal operation, the drain current waveform should stay within the envelope shown.

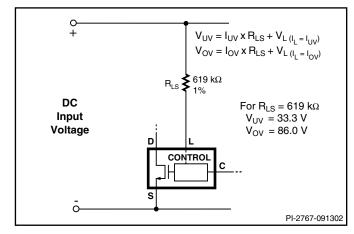

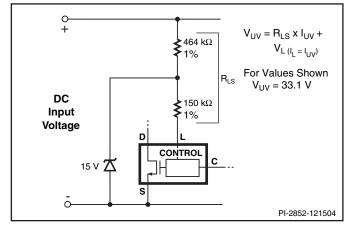

## Line Under-Voltage Detection (UV)

At power up, UV keeps *DPA-Switch* off until the input line voltage reaches the under voltage upper threshold. At power down, UV holds *DPA-Switch* on until the input voltage falls below the under voltage lower threshold. A single resistor connected from the LINE-SENSE pin to the DC input bus sets UV upper and lower thresholds. To avoid false triggering by noise, a hysteresis is implemented which sets the UV lower threshold typically at 94% of the UV upper threshold. If the UV lower threshold is reached during operation without the power supply losing regulation and the condition stays longer than 10 μs (typical), the device will turn off and stay off until the

UV upper threshold has been reached again. Then, a soft-start will be initiated the next time CONTROL pin voltage reaches 5.8.V. If the power supply loses regulation before reaching the UV lower threshold, the device will enter auto-restart. At the end of each auto-restart cycle (S7), the UV comparator is enabled. If the UV upper threshold is not exceeded, the MOSFET will be disabled during the next cycle (see Figure 5). The UV feature can be disabled independent of OV feature.

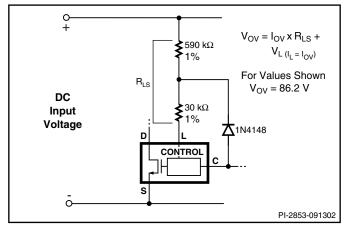

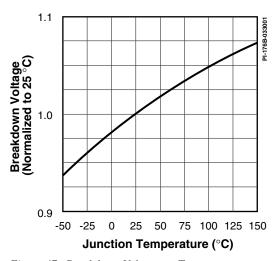

#### Line Overvoltage Shutdown (OV)

The same resistor used for UV also sets an overvoltage threshold which, once exceeded, will force the *DPA-Switch* output into the off-state within one switching cycle. The ratio of OV and UV thresholds is preset at 2.7 as can be seen in Figure 7. When the MOSFET is off, the input voltage surge capability is increased to the voltage rating of the MOSFET (220 V), due to the absence of the reflected voltage and leakage spikes on the drain. A small amount of hysteresis is provided on the OV threshold to prevent noise triggering. The OV feature can be disabled independent of the UV feature as shown in Figure 13.

# Line Feed-Forward with $DC_{MAX}$ Reduction

The same resistor used for UV and OV also implements line voltage feed-forward that minimizes output line ripple and reduces power supply output sensitivity to line transients. This feed-forward operation is illustrated in Figure 4 by the different values of  $I_L$ . Note that for the same CONTROL pin current, higher line voltage results in smaller operating duty cycle. As an added feature, the maximum duty cycle  $DC_{MAX}$  is also reduced from 75% (typical) at a voltage slightly higher than the UV threshold to 33% (typical) at the OV threshold (see Figures 4, 7). Limiting  $DC_{MAX}$  at higher line voltages helps prevent transformer saturation due to large load transients in forward converter applications.  $DC_{MAX}$  of 33% at the OV

threshold was chosen to ensure that the power capability of the *DPA-Switch* is not restricted by this feature under normal operation.

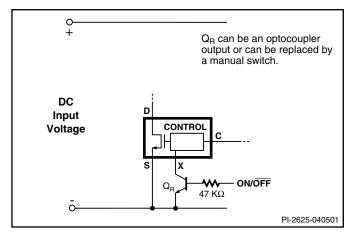

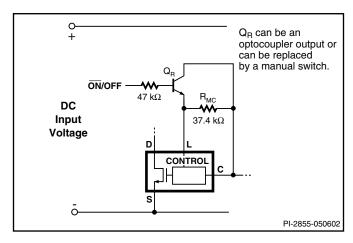

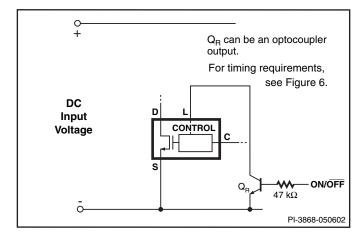

#### Remote ON/OFF

Remote ON/OFF control describes operation where the IC is turned on or off for long periods as opposed to the cycle-by-cycle on/off control, which is described in the Synchronization section below.

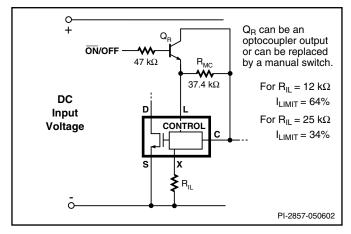

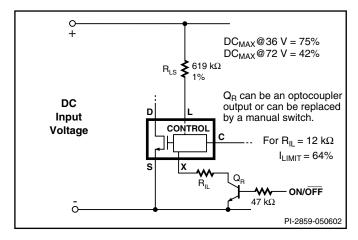

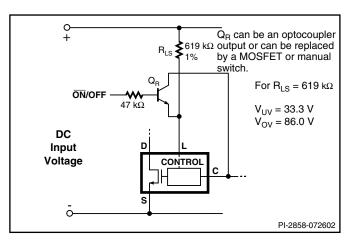

DPA-Switch can be turned on or off by controlling the current into the LINE-SENSE pin or out from the EXTERNAL CURRENT LIMIT pin (see Figure 7). This allows easy implementation of remote ON/OFF control of DPA-Switch in several different ways. A transistor or an optocoupler output connected between the EXTERNAL CURRENT LIMIT pin and the SOURCE pin implements this function with "active-on" (Figures 17, 19 and 21) while a transistor or an optocoupler output connected between the LINE-SENSE pin and the CONTROL pin implements the function with "active-off" (Figures 18, 20 and 22).

When a signal is received at the LINE-SENSE pin or the EXTERNAL CURRENT LIMIT pin to disable the output through any of the pin functions such as OV, UV and remote ON/OFF, *DPA-Switch* always completes its current switching cycle before the output is forced off. The internal oscillator is stopped at the end of the current cycle and stays there as long as the disable signal exists. When the signal at the above pins changes state from disable to enable, the internal oscillator starts the next switching cycle.

The remote ON/OFF feature can be used as a standby or power switch to turn off the *DPA-Switch* and keep it in a very low power consumption state for indefinitely long periods. If the *DPA-Switch* is held in remote-off state for longer than 10 µs

Figure 6. Synchronization Timing Diagram.

(typical), the CONTROL pin goes into the hysteretic mode of operation. In this mode, the CONTROL pin goes through alternate charge and discharge cycles between 4.8 V and 5.8 V (see CONTROL Pin Operation section above) and the IC runs entirely off the high voltage DC input, but with very low power consumption (30 mW typical at 48 V with LINE-SENSE and EXTERNAL CURRENT LIMIT pins open). When the DPA-Switch is remotely turned on after entering this mode, it will initiate a normal start-up sequence with soft-start the next time the CONTROL pin reaches 5.8 V. In the worst case, the delay from remote on to start-up can be equal to the full discharge/charge cycle time of the CONTROL pin, which is approximately 36 ms for a 22 µF CONTROL pin capacitor. This reduced-consumption remote-off mode can eliminate expensive and unreliable in-line mechanical switches. It also allows for microprocessor-controlled turn-on and turn-off sequences that may be required in certain applications.

#### **Synchronization**

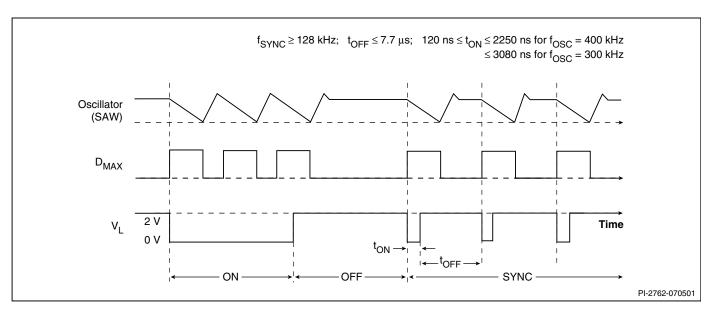

In addition to sensing incoming current for OV, UV and remote ON/OFF, the LINE-SENSE pin also monitors its pin voltage through a 1 V threshold comparator. A pin voltage below 1 V turns on *DPA-Switch*. When the voltage at LINE-SENSE pin rises beyond 1 V to disable the output, DPA-Switch completes its current switching cycle before the output is forced off (similar to remote ON/OFF operation). The internal oscillator is stopped at the end of the current cycle awaiting the LINE-SENSE pin voltage to go low to start the next cycle. This allows the use of the 1 V threshold to synchronize DPA-Switch to an external signal with a frequency lower than its internal switching frequency. A transistor or an optocoupler output connected between the LINE-SENSE pin and the SOURCE pin implements this function (see Figure 24). Please refer to Figure 6 for the timing waveforms of synchronization operation.

In order to be recognized as a synchronization pulse, the LINE-SENSE pin needs to stay low (on-time) for at least 120 ns but no more than 2250 ns for 400 kHz (or 3080 ns for 300 kHz) internal switching frequency. In addition, the off-time must be kept below 7.7  $\mu$ s, which is a limitation set by the lowest synchronization frequency of 128 kHz allowed by the chip. The effective DC<sub>MAX</sub> for synchronization operation can be calculated as 0.75  $\cdot$  f<sub>SYNC</sub>/f<sub>OSC</sub>. An off-time longer than 7.7  $\mu$ s may force the CONTROL pin to go into the hysteretic mode and initiate a soft-start cycle at next turn-on.

#### **Soft-Start**

Two on-chip soft-start functions are activated at start-up with a duration of 5 ms (typical). Maximum duty cycle starts from 0% and linearly increases to the default maximum of 75% at the end of the 5 ms duration and the current limit starts from about 85% and linearly increases to 100% at the end of the 5 ms duration. In addition to start-up, soft-start is also activated

at each restart attempt during auto-restart and when restarting after being in hysteretic regulation of CONTROL pin voltage  $(V_c)$ , due to remote off or thermal shutdown conditions. This effectively minimizes current and voltage stresses on the output MOSFET, the clamp circuit and the output rectifier during start-up. This feature also helps minimize output overshoot and prevents saturation of the transformer during start-up.

#### Shutdown/Auto-Restart

To minimize DPA-Switch power dissipation under fault conditions, the shutdown/auto-restart circuit turns the power supply on and off at an auto-restart duty cycle of typically 4% if an out of regulation condition persists. Loss of regulation interrupts the external current into the CONTROL pin.  $V_{\rm C}$  regulation changes from shunt mode to the hysteretic auto-restart mode as described in CONTROL pin operation section. When the fault condition is removed, the power supply output becomes regulated,  $V_{\rm C}$  regulation returns to shunt mode, and normal operation of the power supply resumes.

#### **Hysteretic Over-Temperature Protection**

Over temperature protection is provided by a precision analog circuit that turns the output MOSFET off when the junction temperature exceeds the thermal shutdown temperature (137 °C typical). When the junction temperature cools to below the hysteretic temperature (110 °C typical), normal operation resumes providing automatic recovery.  $V_{\rm C}$  is regulated in hysteretic mode and a 4.8 V to 5.8 V (typical) sawtooth waveform is present on the CONTROL pin while in thermal shutdown.

#### **Bandgap Reference**

All critical *DPA-Switch* internal voltages are derived from a temperature-compensated bandgap reference. This reference is also used to generate a temperature-compensated current reference that is trimmed to accurately set the switching frequency, current limit, and the line OV/UV thresholds. *DPA-Switch* has improved circuitry to maintain all of the above critical parameters within very tight absolute and temperature tolerances.

#### **High-Voltage Bias Current Source**

This current source biases *DPA-Switch* from the DRAIN pin and charges the CONTROL pin external capacitance during start-up or hysteretic operation. Hysteretic operation occurs during auto-restart, remote off and over-temperature shutdown. In this mode of operation, the current source is switched on and off with an effective duty cycle of approximately 20%. This duty cycle is determined by the ratio of CONTROL pin charge ( $I_{\text{CICH}}$ ) and discharge currents ( $I_{\text{CD1}}$  and  $I_{\text{CD2}}$ ). This current source is turned off during normal operation when the output MOSFET is switching. The effect of the current source switching may be seen on the DRAIN voltage waveform as small disturbances, which is normal.

# **Using Feature Pins**

## FREQUENCY (F) Pin Operation

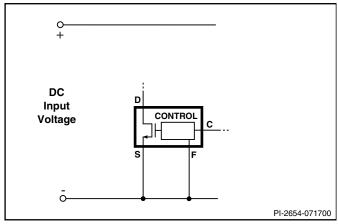

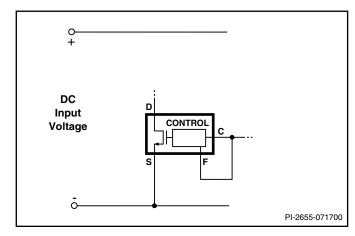

The FREQUENCY pin is a digital input pin. Shorting the FREQUENCY pin to SOURCE pin selects the nominal switching frequency of 400 kHz (Figure 9) which is suited for most applications. For other applications that may benefit from lower switching frequency, a 300 kHz switching frequency can be selected by shorting the FREQUENCY pin to the CONTROL pin (Figure 10). This pin should not be left open.

#### LINE-SENSE (L) Pin Operation

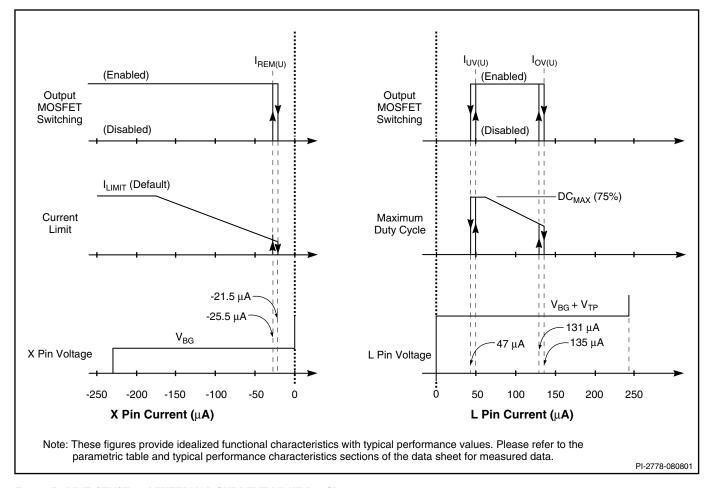

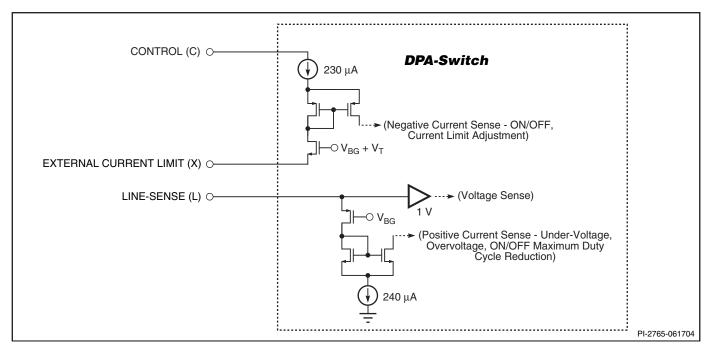

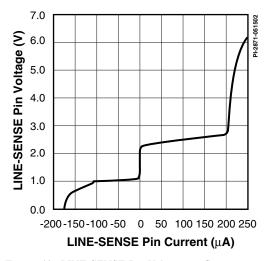

When current is fed into the LINE-SENSE pin, it works as a voltage source of approximately 2.6 V up to a maximum current of +240  $\mu$ A (typical). At +240  $\mu$ A, this pin turns into a constant current sink. Refer to Figure 8. In addition, a comparator with a threshold of 1 V is connected at the pin and is used to detect when the pin is shorted to the SOURCE pin.

There are a total of five functions available through the use of the LINE-SENSE pin: OV, UV, line feed-forward with  $DC_{MAX}$ reduction, remote ON/OFF and synchronization. Shorting the LINE-SENSE pin to the SOURCE pin disables all five functions. The LINE-SENSE pin is typically used for line sensing by connecting a resistor from this pin to the positive input DC voltage bus to implement OV, UV and line feed-forward with DC<sub>MAX</sub> reduction over line voltage. In this mode, the value of the resistor determines the line OV/UV thresholds, and the DC<sub>MAX</sub> is reduced linearly with input DC high voltage starting from just above the UV threshold. This pin can also be used as the input pin for remote ON/OFF and synchronization. An external transistor placed between the LINE-SENSE pin and the CONTROL pin realizes remote ON/OFF via UV or OV threshold. Synchronization is available by connecting an open drain external MOSFET between the LINE-SENSE

pin and the SOURCE pin to generate synchronization pulse. Each time the MOSFET turns on, the falling edge of the LINE-SENSE pin voltage initiates a new switching cycle. The lowest synchronization frequency guaranteed by DPA-Switch is 128 kHz. Refer to Table 2 for possible combinations of the functions with example circuits shown in Figure 11 through Figure 24. A description of specific functions in terms of the LINE-SENSE pin I/V characteristic is shown in Figure 7 (right hand side). The horizontal axis represents LINE-SENSE pin current with positive polarity indicating currents flowing into the pin. The meaning of the vertical axes varies with functions. For those that control the on/off states of the output such as UV, OV and remote ON/OFF, the vertical axis represents the enable/disable states of the output. UV triggers at  $I_{\scriptscriptstyle \rm UV}$ (+50  $\mu$ A typical with 4  $\mu$ A hysteresis) and OV triggers at  $I_{ov}$ (+135 μA typical with 4 μA hysteresis). Between the UV and OV thresholds, the output is enabled. For line feed-forward with  $\operatorname{DC}_{\operatorname{MAX}}$  reduction, the vertical axis represents the magnitude of the DC<sub>MAX</sub> Line feed-forward with DC<sub>MAX</sub> reduction lowers maximum duty cycle from 75% at  $I_{L(DC)}$  (+55  $\mu A$  typical) to 33% at  $I_{ov}$  (+135  $\mu$ A).

## **EXTERNAL CURRENT LIMIT (X) Pin Operation**

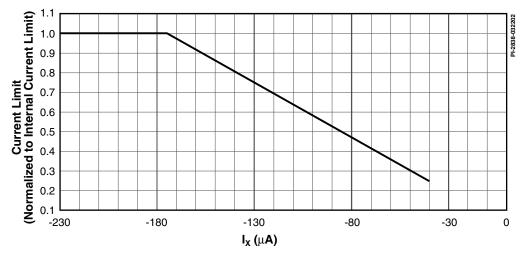

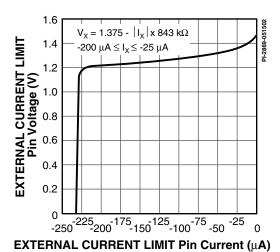

When current is drawn out of the EXTERNAL CURRENT LIMIT pin, it works as a voltage source of approximately 1.3 V up to a maximum current of -230  $\mu$ A (typical). At -230  $\mu$ A, it turns into a constant current source (refer to Figure 8).

There are two functions available through the use of the EXTERNAL CURRENT LIMIT pin: external current limit and remote ON/OFF. Shorting the EXTERNAL CURRENT LIMIT pin and SOURCE pin disables both functions. In high efficiency applications, this pin can be used to reduce the current limit externally to a value close to the operating peak current, by connecting the pin to the SOURCE pin through a resistor.

| LINE-SE                                    | NSE    | AND   | EXT    | ERN   | AL CI  | JRRE    | ENT I   | _IMIT   | PIN     | TAB      | LE*     |     |    |    |

|--------------------------------------------|--------|-------|--------|-------|--------|---------|---------|---------|---------|----------|---------|-----|----|----|

| Figure Number ▶                            | 11     | 12    | 13     | 14    | 15     | 16      | 17      | 18      | 19      | 20       | 21      | 22  | 23 | 24 |

| Three Terminal Operation                   | 1      |       |        |       |        |         |         |         |         |          |         |     |    |    |

| Under-Voltage                              |        | 1     | 1      |       |        |         |         |         |         |          | 1       | 1   | 1  |    |

| Overvoltage                                |        | 1     |        | 1     |        |         |         |         |         |          | 1       | 1   | 1  |    |

| Line Feed-Forward (DC <sub>MAX</sub> )     |        | 1     |        |       |        |         |         |         |         |          | 1       | 1   | 1  |    |

| Overload Power Limiting                    |        |       |        |       |        | 1       |         |         |         |          |         |     |    |    |

| External Current Limit                     |        |       |        |       | 1      | 1       |         |         | 1       | 1        | 1       |     | 1  |    |

| Remote ON/OFF                              |        |       |        |       |        |         | 1       | 1       | 1       | 1        | 1       | 1   |    |    |

| Synchronization                            |        |       |        |       |        |         |         |         |         |          |         |     |    | 1  |

| *This table is only a partial list of many | LINE-S | SENSE | and EX | TERNA | L CURF | RENT LI | MIT pin | configu | rations | that are | possibl | le. |    |    |

Table 2. Typical LINE-SENSE and EXTERNAL CURRENT LIMIT Pin Configurations.

Figure 7. LINE-SENSE and EXTERNAL CURRENT LIMIT Pin Characteristics.

The pin can also be used as a remote ON/OFF control input. Table 2 shows several different ways of using this pin. See Figure 7 for a description of the functions where the horizontal axis (left hand side) represents the EXTERNAL CURRENT LIMIT pin current. The meaning of the vertical axes varies with function. For those that control the on/off states of the

output such as remote ON/OFF, the vertical axis represents the enable/disable states of the output. For external current limit, the vertical axis represents the magnitude of the  $I_{\text{LIMIT}}$  Please see graphs in the Typical Performance Characteristics section for the current limit programming range and the selection of the appropriate resistor value.

Figure 8. LINE-SENSE (L), and EXTERNAL CURRENT LIMIT (X) Pin Input Simplified Schematic.

# Typical Uses of FREQUENCY (F) Pin

Figure 10. 300 kHz Frequency Operation.

## Figure 9. 400 kHz Frequency Operation.

# Typical Uses of LINE-SENSE (L) and EXTERNAL CURRENT LIMIT (X) Pins

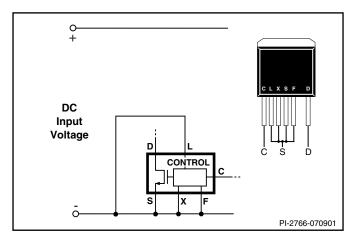

Figure 11. Three Terminal Operation (LINE-SENSE and EXTERNAL CURRENT LIMIT Features Disabled. FREQUENCY Pin can be tied to SOURCE or CONTROL Pin).

Figure 12. Line-Sensing for Under-Voltage, Overvoltage and Line Feed-forward.

Figure 13. Line-Sensing for Under-Voltage Only (Overvoltage Disabled).

Figure 14. Line-Sensing for Overvoltage Only (Under-Voltage Disabled). Maximum Duty Cycle will be reduced at Low Line.

# Typical Uses of LINE-SENSE (L) and EXTERNAL CURRENT LIMIT (X) Pins (cont.)

Figure 15. Externally Set Current Limit.

Figure 16. Current Limit Reduction with Line Voltage.

Figure 17. Active-on (Fail Safe) Remote ON/OFF.

Figure 18. Active-off Remote ON/OFF. Maximum Duty Cycle will be reduced.

Figure 19. Active-on Remote ON/OFF with Externally Set Current Limit.

Figure 20. Active-off Remote ON/OFF with Externally Set Current

# Typical Uses of LINE-SENSE (L) and EXTERNAL CURRENT LIMIT (X) Pins (cont.)

Figure 21. Active-on Remote ON/OFF with LINE-SENSE and EXTERNAL CURRENT LIMIT.

Figure 22. Active-off Remote ON/OFF with LINE-SENSE.

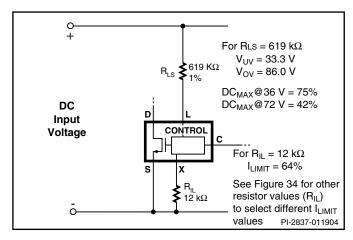

Figure 23. Line-Sensing and Externally Set Current Limit.

Figure 24. Synchronization.

# **Application Examples**

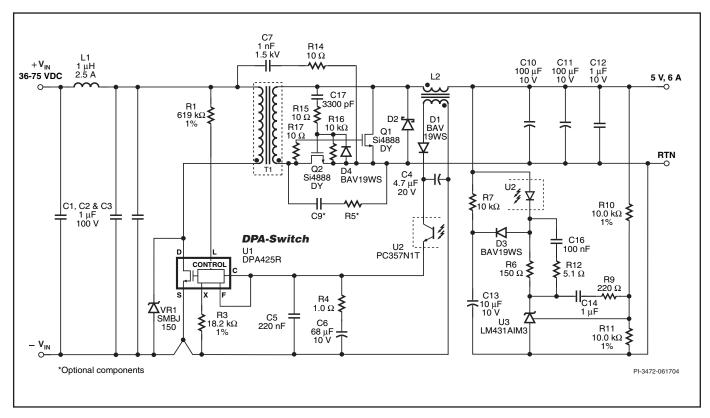

Figure 25. A High Efficiency 30 W, 5 V, Telecom Input DC-DC Converter.

#### **High Efficiency 30 W Forward Converter**

The circuit shown in Figure 25 is a typical implementation of a single output DC-DC converter using *DPA-Switch* in a forward configuration with synchronous rectification. This design delivers 30 W at 5 V, from a 36 VDC to 75 VDC input with a nominal efficiency at 48 VDC of 90% using the DPA425R.

By taking advantage of many of the built-in features of the *DPA-Switch*, the design is greatly simplified compared to a discrete implementation. Resistor R1 programs the input undervoltage and overvoltage thresholds to typically 33 V and 86 V respectively. This resistor also linearly reduces the maximum duty from the internal maximum of 75% at 36 V to 42% at 72 V to prevent core saturation during load transients at high input voltages. The *DPA-Switch* internal thresholds are toleranced and characterized so the designer can guarantee the converter will begin operation at 36 V, necessary to meet ETSI standards, without the cost of an external reference IC.

The current limit is externally set by resistor R3 to just above the drain current level needed for maximum load regulation to limit the maximum overload power of the converter. The externally programmable current limit feature also allows a larger *DPA-Switch* family member to be selected. Using the X pin, the current limit can be adjusted to the same level. A large device reduces conduction losses and improves efficiency without

requiring any other circuit changes. This has been used here to replace the DPA424R with a DPA425R.

The selectable 300/400 kHz switching frequency is set to 300 kHz by connecting the FREQUENCY (F) pin to CONTROL (C).

DRAIN voltage clamping is provided by VR1, which keeps the peak DRAIN voltage within acceptable limits. Transformer core reset is provided by the gate capacitance of Q1 with R17 in series. Optional reset capacitance C9 with R5 can be added if necessary to supplement the gate capacitance of Q1.

The output of the transformer is rectified using MOSFETs to provide synchronous rectification. The UV/OV function, together with the turns ratio of the transformer, defines the maximum MOSFET gate voltage, allowing the very simple gate drive arrangement, without the need for drive windings or a drive IC. During primary on-time, capacitor C17 couples charge through resistor R15 to drive the gate of the forward MOSFET, Q2. Capacitor C17 provides a DC isolated drive for Q2, preventing gate overstress on Q1 during power down. The time constant formed by R16 and C17 is selected to be much longer than one switching cycle. Diode D4 resets the voltage on capacitor C17 before the next switching cycle. During the primary off-time, the diode D2 provides a conduction path for the energy in inductor L2 while Q1 is still off. The transformer

Figure 26. A Cost Effective 6.6 W, 3.3 V Flyback DC-DC Converter.

reset voltage on the secondary winding directly drives a positive voltage on the gate of catch MOSFET, Q1. MOSFET Q1 provides a low loss conduction path for a substantial portion of the primary off-time. An isolated auxiliary winding on L2, rectified and filtered by D1 and C4, provides the bias supply for the optocoupler transistor. Output regulation is achieved by using secondary side voltage reference, U3. The resistor divider formed by R10 and R11, together with the reference voltage, determines the output voltage. Diode D3 and C13 form a soft-finish network that, together with the internal duty cycle and current limit soft-start of the DPA-Switch, prevent output overshoot at start-up. Resistor R7 ensures that the soft-finish capacitor is discharged quickly when the output falls out of regulation. Control loop response is shaped by R6, C16, R12, C14, R9, R4 and C5, providing a wide bandwidth and good phase margin at gain crossover. Since the PWM control in DPA-Switch is voltage mode, no slope compensation is required for duty cycles above 50%.

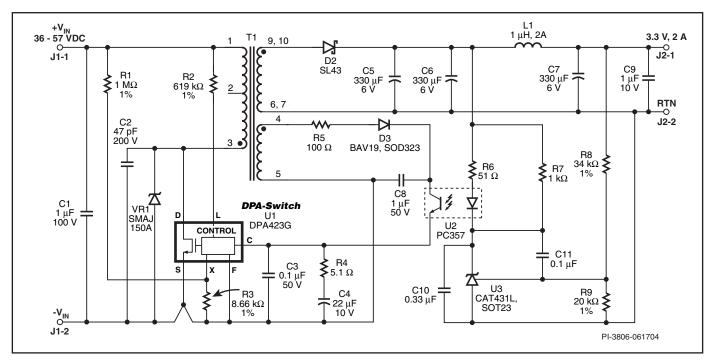

## Cost Effective 6.6 W Flyback Converter

The *DPA-Switch* flyback power supply provides a cost effective solution for high density PoE and VoIP DC-DC applications.

Figure 26 shows a typical implementation of a single output flyback converter using the DPA423G. For applications that require input to output isolation, this simple, low component count design delivers 6.6 W at 3.3 V from a 36 VDC to 57 VDC input with a nominal efficiency at 48 VDC of 80%.

Resistor R2 programs the input under-voltage and overvoltage thresholds to 33 V and 86 V respectively. Resistors R1 and R3 program the internal device current limit. The addition of line

sense resistor R1 reduces the current limit with increasing input voltage, preventing excessive overload output current. In this design the overload output current varies less than  $\pm 2.5\%$  across the entire input voltage range. Controlling the current limit also reduces secondary component stress and leakage inductance spikes, allowing the use of a lower  $V_{\rm RRM}$  (30 V rather than 40 V) Schottky output diode, D2.

The primary side Zener clamp VR1 ensures the peak drain voltage is kept below the 220 V  $BV_{DSS}$  rating of U1 under input surge and overvoltage events. During normal operation, VR1 does not conduct and C2 is sufficient to limit the peak drain voltage.

The primary bias winding provides CONTROL pin current after start-up. Diode D3 rectifies the bias winding, while components R5 and C8 reduce high frequency switching noise and prevent peak charging of the bias voltage. Capacitor C3 provides local decoupling of U1 and should be physically close to the CONTROL and SOURCE pins. Energy storage for start-up and auto-restart timing is provided by C4.

The secondary is rectified by D2 and the Low ESR tantalum output capacitors, C5-C7, minimizing switching ripple and maximizing efficiency. A small footprint secondary output choke L1 and ceramic output capacitor C9 are adequate to reduce high frequency noise and ripple to below 35 mV peak-peak under full load conditions.

The output voltage is sensed by the voltage divider formed by resistors R8 and R9 and is fed to the low voltage 1.24 V reference U3. Feedback compensation is provided by R6, R7

Figure 27. PoE Interface Circuit Using a Bipolar Transistor Pass-Switch and DPA424P.

and C11 together with C4 and R4. Capacitor C10 provides a soft-finish characteristic, preventing output overshoot during start-up.

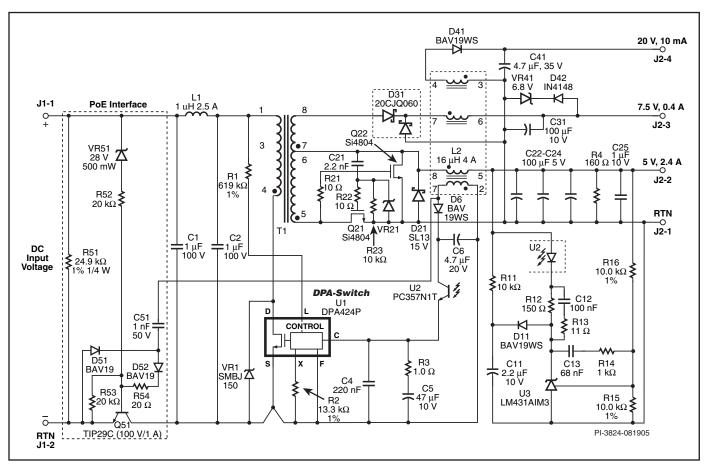

## **Low Cost PoE VoIP Phone Converter**

The basic circuitry to support IEEE standard 802.3af Power over Ethernet (PoE) is straightforward. Class 0 signature and classification circuits can be implemented with a single resistor and the required under-voltage lockout function is a voltage controlled pass-switch. By adding this circuitry to the front end of a DPA converter, a low cost and low component count PoE powered device (PD) power supply can be implemented. Figure 27 shows a typical PD solution.

The PoE specification requires the PD to provide three fundamental functions: discovery, classification, and pass-switch connection.

When input voltage is applied to the PD, it must present the correct discovery signature impedance in the voltage range of

2.5 VDC to 10 VDC. This impedance is provided by R51 in Figure 27.

The second "classification" phase occurs at input voltages 15 VDC to 20 VDC. The PD must draw a specified current to identify the device class (Class 0 specifies 0.5 mA to 4 mA). This is again accomplished by resistor R51.

In the third phase, the bipolar pass-switch (Q51 in Figure 27) connects the input voltage to the power supply at voltages above approximately 30 VDC (28 V+VR52). Zener diode VR51 conducts, driving the current through resistor R52 to the base of Q51. Resistor R53 prevents turn-on under other conditions. Once the Power supply has started, components D51, D52, C51 and R54 enhance the base-current drive by coupling power from the power supply bias winding.

Once the three start up phases have been successfully completed, the *DPA-Switch* is allowed to function as a forward converter (described in Figure 25 and accompanying text).

# **Key Application Considerations**

## **DPA-Switch** Design Considerations

#### **Power Table**

This section provides a description of the assumptions used to generate the power tables (Tables 1 and 3 through 6) and explains how to use the information provided by them.

All Power tables: Tables 1 and 3 through 6

- Maximum output power is limited by the device internal current limit. This is the peak output power which could become the continuous output power, provided adequate heat sinking is used.

- Data assumes adequate heat sinking to keep the junction temperature at or below 100 °C and worst case  $R_{\rm DS(ON)}$  at  $T_{\rm r}$  = 100 °C.

- The use of P and G packages are recommended for device dissipation equal to or less than 1.5 W only due to package thermal limitation. For device dissipation above 1.5 W, use S and R packages.

Forward power tables: Tables 1 (upper half), 3 and 4

- Output power figures are based on forward topology using Schottky diode rectification. Up to 5% higher output power is possible using synchronous rectification.

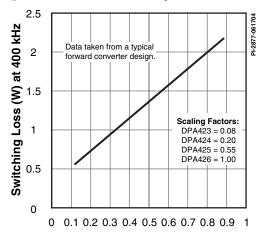

- Dissipation data assumes a diode loss representing 6% of the total output power and combined loss in magnetic components representing 6% of the total output power. DPA-Switch losses are based on a ratio between conduction and switching losses of approximately 3:1. These assumptions are typical for a single 5 V output forward converter design using Schottky rectification and adequately designed magnetic components.

Flyback power tables: Tables 1 (lower half), 5 and 6

- Output power and dissipation figures are based on a 5 V output using Schottky diode rectification with an efficiency of 85%. Values are generated by calculation based on I<sup>2</sup> R<sub>DS(ON)</sub> losses and characterization of switching losses, correlated to bench measurement of each *DPA-Switch* device.

- Device dissipations above 1.5 W are possible using the S and R packages. However the forward converter topology is recommended for such higher power designs.

The power tables provide two types of information. The first is the expected device dissipation for a given output power. The second is the maximum power output. Each table specifies the input voltage range and assumes a single 5 V output using Schottky diode rectification.

For example, referring to Table 1, for 36 VDC to 75 VDC input range, DPA424 would typically dissipate 1 W in a 23 W forward converter and has a maximum power capacity of 35 W. In the

| (                                                              | OUTPUT POWER TABLE |        |      |      |      |        |  |  |  |  |

|----------------------------------------------------------------|--------------------|--------|------|------|------|--------|--|--|--|--|

| 16-32 VDC RANGE (FORWARD) <sup>2</sup>                         |                    |        |      |      |      |        |  |  |  |  |

| Total Device Dissipation 0.5 W 1 W 2.5 W 4 W 6 W Power Output¹ |                    |        |      |      |      |        |  |  |  |  |

| DPA423                                                         | 5 W                | 7 W    | -    | -    | -    | 7.5 W  |  |  |  |  |

| DPA424                                                         | 7 W                | 10 W   | 15 W | -    | -    | 15.5 W |  |  |  |  |

| DPA425                                                         | 10 W               | 14 W   | 22 W | 27 W |      | 31 W   |  |  |  |  |

| DPA426                                                         | 12 W               | 16.5 W | 25 W | 31 W | 37 W | 43 W   |  |  |  |  |

Table 3. Output Power Table for 16-32 VDC Input Voltage. Notes: 1. Limited by device internal current limit. 2. See text in this section for a complete description of assumptions. 3. See Part Ordering Information.

| OUTPUT POWER TABLE          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |        |      |      |                     |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|---------------------|--|--|--|

| 24                          | 24-48 VDC RANGE (FORWARD) <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |        |      |      |                     |  |  |  |

| Total Device<br>Dissipation | The state of the s |      |        |      |      |                     |  |  |  |

| PRODUCT <sup>3</sup>        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |        |      |      | Output <sup>1</sup> |  |  |  |

| DPA423                      | 8 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 W | -      | ı    | ı    | 11.5 W              |  |  |  |

| DPA424                      | 11 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16 W | 23.5 W | ı    | -    | 25 W                |  |  |  |

| DPA425                      | 16 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22 W | 35 W   | 43 W |      | 47 W                |  |  |  |

| DPA426                      | 18 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 W | 39 W   | 48 W | 58 W | 65 W                |  |  |  |

Table 4. Output Power Table for 24-48 VDC Input Voltage (See Table 3 for Notes).

| 0                           | OUTPUT POWER TABLE                     |       |      |      |                     |  |  |  |  |  |

|-----------------------------|----------------------------------------|-------|------|------|---------------------|--|--|--|--|--|

| 16                          | 16-32 VDC RANGE (FLYBACK) <sup>2</sup> |       |      |      |                     |  |  |  |  |  |

| Total Device<br>Dissipation |                                        |       |      |      |                     |  |  |  |  |  |

| PRODUCT <sup>3</sup>        |                                        |       |      |      | Output <sup>1</sup> |  |  |  |  |  |

| DPA423                      | 5 W                                    | -     | -    | -    | 6 W                 |  |  |  |  |  |

| DPA424                      | 6.5 W                                  | 8.5 W | 10 W | -    | 11 W                |  |  |  |  |  |

| DPA425                      | 7 W                                    | 10 W  | 12 W | 15 W | 22 W                |  |  |  |  |  |

Table 5. Flyback Output Power Table for 16-32 VDC Input Voltage (See Table 3 for Notes).

| OUTPUT POWER TABLE                     |                              |        |      |   |                     |  |  |  |  |

|----------------------------------------|------------------------------|--------|------|---|---------------------|--|--|--|--|

| 24-48 VDC RANGE (FLYBACK) <sup>2</sup> |                              |        |      |   |                     |  |  |  |  |

| Total Device<br>Dissipation            | 0.5 W 0.75 W 1 W 1.5 W Power |        |      |   |                     |  |  |  |  |

| PRODUCT <sup>3,4</sup>                 |                              |        |      |   | Output <sup>1</sup> |  |  |  |  |

| DPA423                                 | 7 W                          | -      | -    | - | 8.5 W               |  |  |  |  |

| DPA424                                 | 8.5 W                        | 11.5 W | 14 W | - | 17 W                |  |  |  |  |

Table 6. Flyback Output Power Table for 24-48 VDC Input Voltage. Notes: 1. Maximum output power is limited by device internal current limit. 2. See text in this section for a complete description of assumptions. 3. See Part Ordering Information. 4. Higher switching losses may prevent DPA425 from delivering more power than a smaller device.

same converter, DPA425 would dissipate 0.5 W. Selecting DPA425 with associated reduced dissipation would increase overall converter efficiency by approximately 2%.

Issues Affecting Dissipation:

- 1) Using synchronous rectification will tend to reduce device dissipation.

- Designs with lower output voltages and higher currents will tend to increase the device dissipation listed in the power table.

- 3) Reduced input voltage decreases the available output power for the same device dissipation. Tables 3 to 6 are the power tables for 16 VDC and 24 VDC input voltages. Input voltages below 16 V are possible, but since the internal start-up current source is not specified at voltages below 16 V, an external chip supply current should be fed into the CONTROL pin approximately equal to but less than I<sub>CDI</sub>.

#### **DPA-Switch** Selection

Use Tables 1 and 3 through 6 to select the *DPA-Switch* based on device dissipation. Selecting the optimum *DPA-Switch* depends upon required maximum output power, efficiency, heat sinking constraints and cost goals. With the option to externally reduce current limit, a larger *DPA-Switch* may be used for lower power applications where higher efficiency is needed or minimal heat sinking is available. Generally, selecting the next larger device, than is required for power delivery will give the highest efficiency. Selecting even larger devices may give little or no improvement in efficiency due to the improvement in conduction losses being negated by larger device switching losses. Figure 50 provides information on switching losses. This together with conduction loss calculations give an estimate of device dissipation.

## **Primary Clamp**

A primary clamp network is recommended to keep the peak DRAIN voltage due to primary leakage inductance to below the  $\mathrm{BV}_{\mathrm{DSS}}$  specification. A Zener diode combined with a small value capacitor connected across the primary winding is a low cost and low part count implementation.

#### **Output Rectification**

Rectification of the secondary is typically performed using Schottky diodes or synchronous rectification. Schottky diodes are selected for peak inverse voltage, output current, forward drop and thermal conditions. Synchronous rectification requires the additional complication of providing gate drive. The specified line under-voltage and line overvoltage thresholds of *DPA-Switch* simplifies deriving gate drive directly from the transformer secondary winding for many applications. The turns ratio of the transformer together with the under/overvoltage thresholds defines the minimum and maximum gate voltages, removing the need for Zeners to clamp the gate voltage.

#### **Soft-Start**

Generally a power supply experiences maximum stress at start-up before the feedback loop achieves regulation. For a period of 5 ms the on-chip soft-start linearly increases the duty cycle from zero to the default DC<sub>MAX</sub> at turn-on. In addition, the primary current limit increases from 85% to 100% over the same period. This causes the output voltage to rise in an orderly manner allowing time for the feedback loop to take control of the duty cycle. This integrated soft-start reduces the stress on the *DPA-Switch* MOSFET, clamp circuit and output diode(s), and helps prevent transformer saturation during start-up. Also, soft-start limits the amount of output voltage overshoot, and in many applications eliminates the need for a soft-finish capacitor. If necessary, to remove output overshoot, a soft-finish capacitor may be added to the secondary reference.

## **Switching Frequency**

The FREQUENCY pin of *DPA-Switch* offers a switching frequency option of 400 kHz or 300 kHz. Operating at 300 kHz will increase the amount of magnetization energy stored in the transformer. This is ideal for applications using synchronous rectification driven directly from the transformer secondary where this energy can be used to drive the catch MOSFET gate.

#### **Transformer Design**

It is recommended that the forward converter transformer be designed for maximum operating flux swing of 1500 Gauss and a peak flux density of 3500 Gauss. When operating at the maximum current limit of the selected *DPA-Switch* (during overload conditions), neither magnetic component (transformer and output inductor) should be allowed to saturate. When a larger device than necessary has been selected, reducing the internal current limit close to the operating peak current limits overload power and minimizes the size of the secondary components.

#### No-load and Standby Consumption

Cycle skipping operation at light or no load can significantly reduce power loss. In addition this operating mode ensures that the output maintains regulation even without an external minimum load. However, if cycle skipping is undesirable in a particular application, it can be avoided by adding sufficient pre-load.

### **DPA-Switch** Layout Considerations

The *DPA-Switch* can operate with large DRAIN current, the following guidelines should be carefully followed.

#### **Primary Side Connections**

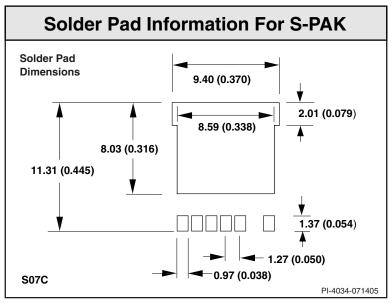

The tab of *DPA-Switch* R package and S-PAK is the intended return path for the high switching currents. Therefore, the tab should be connected by wide, low impedance traces back to

the input decoupling capacitor. The SOURCE pin should not be used to return the power currents; incorrect operation of the device may result. The SOURCE is only intended as a signal ground. The device tab (SOURCE) is the correct connection for high current with the R package and S-PAK.