CMOS LSI

## **DTMF Receiver LSI**

# **Applications**

• Remote controllers for telephone answering machines and other telephone products

## **Features**

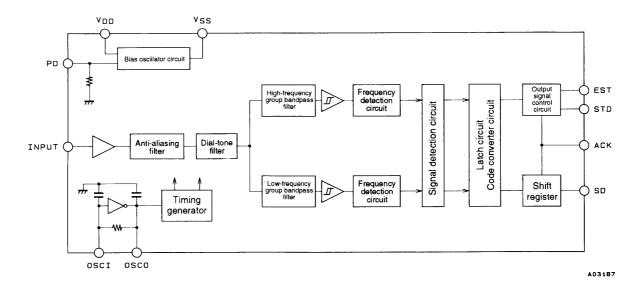

- Detects 16 DTMF signals.

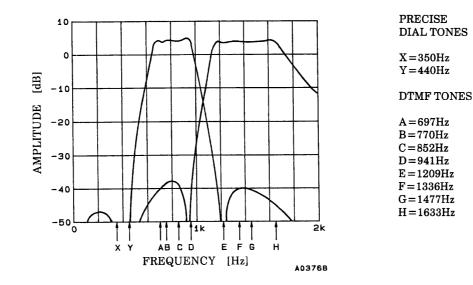

- Includes on-chip all filters required in a DTMF receiver — Dial-tone filter

- High-frequency group bandpass filter

- Low-frequency group bandpass filter

- Serial data output

- Supports microprocessor-controlled guard times.

- Wide operating power-supply voltage range: 2.7 to 5.5 V

- Supports a low power mode that allows current dissipation to be reduced.

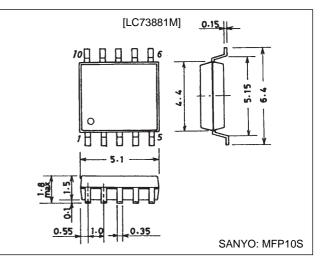

# **Package Dimensions**

unit: mm

### 3086A-MFP10S

## **Specifications**

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions | Ratings                       | Unit |

|-----------------------------|---------------------|------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |            | -0.3 to + 6.0                 | V    |

| Input voltage               | V <sub>IN</sub>     |            | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Input current               | I <sub>IN</sub>     |            | -10 to +10                    | mA   |

| Output voltage              | V <sub>OUT</sub>    |            | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max              | Ta ≤ 70°C  | 120                           | mW   |

| Operating temperature       | Topr                |            | -35 to +70                    | °C   |

| Storage temperature         | Tstg                |            | -50 to +125                   | °C   |

## Allowable Operating Ranges at Ta=-35 to $+70^\circ C,\,V_{SS}$ = 0 V

| Parameter                | Symbol          | Conditions | min                  | typ | max                  | Unit |

|--------------------------|-----------------|------------|----------------------|-----|----------------------|------|

| Operating supply voltage | V <sub>DD</sub> |            | 2.7                  |     | 5.5                  | V    |

| Input high lovel voltage | V <sub>IH</sub> | Pin 7      | 0.7 V <sub>DD</sub>  |     |                      | V    |

| Input high-level voltage |                 | Pin 2      | 0.85 V <sub>DD</sub> |     |                      | V    |

| Input low-level voltage  | V <sub>IL</sub> | Pin 7      |                      |     | 0.3 V <sub>DD</sub>  | V    |

|                          |                 | Pin 2      |                      |     | 0.15 V <sub>DD</sub> | V    |

### DC Electrical Characteristics at Ta = 25°C, $V_{DD}$ = 3 V, $V_{SS}$ = 0 V

| Parameter                  | Symbol Conditions    |                                           | min | typ | max  | Unit |

|----------------------------|----------------------|-------------------------------------------|-----|-----|------|------|

| Operating supply current   | I <sub>DD</sub> (op) |                                           |     | 1.6 | 2.8  | mA   |

| Standby supply current     | I <sub>DD</sub> (st) | PD pin = 3 V                              |     |     | 20   | μA   |

| Output high-level current  | I <sub>OH</sub>      | Pins 6, 8 and 9, V <sub>OUT</sub> = 2.6 V |     |     | -0.3 | mA   |

| Output low-level current   | I <sub>OL</sub>      | Pins 6, 8 and 9, $V_{OUT}$ = 0.4 V        | 0.6 |     |      | mA   |

| Input impedance            | Zin                  | Pin 1                                     | 10  |     |      | kΩ   |

| Pull-down resistor current | I <sub>SI</sub>      | PD = 3 V                                  |     | 1.2 | 3.0  | μA   |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

| Parameter                      | Symbol           | Conditions                  | min       | typ      | max      | Unit |

|--------------------------------|------------------|-----------------------------|-----------|----------|----------|------|

| Input signal valid level       | _                | *1, 2, 3, 5, 6, 9           | -45       |          | -20      | dBm  |

| Positive twist accept          | _                | *2, 3, 6, 9, 11             |           | ±10      |          | dB   |

| Frequency detection accept     | _                | *2, 3, 5, 9                 | ±1.5% ± 2 |          |          | Hz   |

| Frequency rejection accept     | _                | *2, 3, 5                    | ±3.5      |          |          | %    |

| Third tone tolerance           | _                | *2, 3, 4, 5, 9, 10          |           | -16      |          | dB   |

| Dial tone tolerance            | _                | *2, 3, 4, 5, 8, 9, 10       |           | +22      |          | dB   |

| Noise tolerance                | _                | *2, 3, 4, 5, 7, 9, 10       |           | -8       |          | dB   |

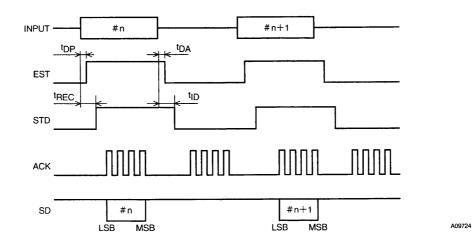

| Tone present detection time    | t <sub>DP</sub>  | See the timing chart.       | 3         |          | 20       | ms   |

| Tone absent detection time     | t <sub>DA</sub>  | See the timing chart.       | 0.5       |          | 20       | ms   |

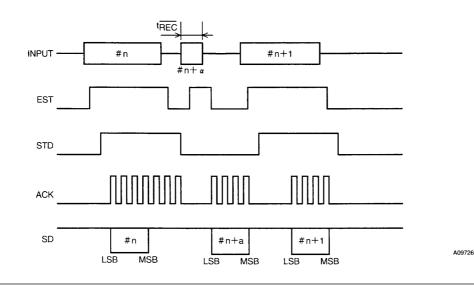

| Tone duration accept           | t <sub>REC</sub> | See the timing chart.       |           |          | 20       | ms   |

| Tone duration reject           | t <sub>REC</sub> | See the timing chart.       | 45        |          |          | ms   |

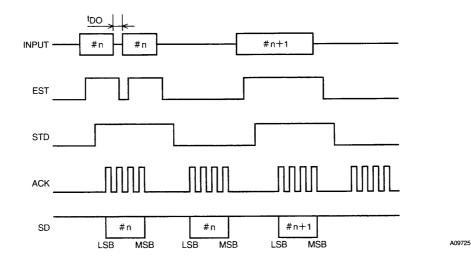

| Inter-digit pause invalid time | t <sub>DO</sub>  | See the timing chart.       |           |          | 20       | ms   |

| Inter-digit pause valid time   | t <sub>ID</sub>  | See the timing chart.       | 40        |          |          | ms   |

| Data shift speed               | _                |                             |           |          | 1        | MHz  |

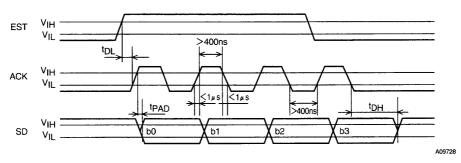

| Data output delay time         | t <sub>PAD</sub> | See the ACK/SD timing chart |           | 100      |          | ns   |

| Setup time delay               | t <sub>DL</sub>  | See the ACK/SD timing chart | 4         |          |          | μs   |

| Data hold time                 | t <sub>DH</sub>  | See the ACK/SD timing chart | 30        |          |          | ns   |

| Oscillator frequency           | fosc             |                             | 4.190109  | 4.194304 | 4.198498 | MHz  |

| Load capacitance               | C <sub>XO</sub>  | The OSCI and OSCO pins      |           |          | 30       | pF   |

Note: 1. The dBm values are defined such that 0 dBm is the 1 mW power level for a 600  $\Omega$  load.

2. All 16 DTMF signals frequency

3. With a 40 ms DTMF signal period and a 40 ms pause period

With a 40 ms DTMF signal period and a 40 ms pause p

Nominal DTMF signal frequencies

Low-group and high-group signal levels are the same.

DTMF signal frequency deviations within ±1.5% ± 2 Hz

7. Gaussian noise with a 0 to 3 kHz bandwidth

8. 350 and 440 Hz dial tone frequencies

9. Error rate of less than 1 error in 10,000 events

10.Referenced to the lowest component of the DTMF signal.

11.Twist = High-frequency group tone level Low-frequency group tone level

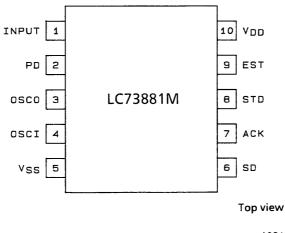

#### **Pin Assignment**

A03186

### **Pin Functions**

| Pin No. | Symbol          | I/O | Function                                                                                                                                                                                                                                     |  |  |

|---------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

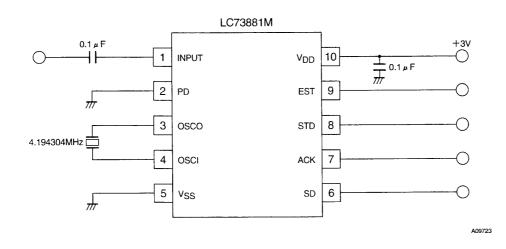

| 1       | INPUT           | 1   | The input must be capacitor coupled. This signal is biased to V <sub>DD</sub> /2 internally.                                                                                                                                                 |  |  |

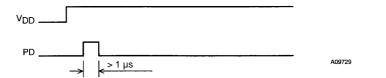

| 2       | PD              | 1   | The LC73881M goes to low power mode when this pin is set high.                                                                                                                                                                               |  |  |

| 3       | OSCO            | 0   | Connect a 4.194304 MHz crystal oscillator or ceramic resonator to these pins to from an oscillator circuit.                                                                                                                                  |  |  |

| 4       | OSCI            | 1   | When using a ceramic resonator, a capacitor of approximately 30 pF must be connected to each pin.                                                                                                                                            |  |  |

| 5       | V <sub>SS</sub> |     | Power supply pin. Normally 0 V.                                                                                                                                                                                                              |  |  |

| 6       | SD              | 0   | The decoded DTMF signal is output, this pin in a 4-bit LSB first format.                                                                                                                                                                     |  |  |

| 7       | ACK             | I   | The ACK pin is used to shift out data from the SD pin. Four pulses are required to shift out the DTMF character, which consists of four bits. The rising edge of the first pulse latches the data (before shifting) into the shift register. |  |  |

| 8       | STD             | 0   | A high level indicates the presence of a DTMF signal. Although the rise of this signal is later than that of the EST pin, it is less sensitive to burst waveforms and other noise.                                                           |  |  |

| 9       | EST             | 0   | A high level indicates the presence of a DTMF signal. Applications should monitor this pin and, after waiting an appropriate period, apply four pulses to the ACK pin to access the data.                                                    |  |  |

| 10      | V <sub>DD</sub> |     | Power supply pin. Normally 2.7 to 5.5 V.                                                                                                                                                                                                     |  |  |

### **Block Diagram**

### **Test Circuit, Sample Application Circuit**

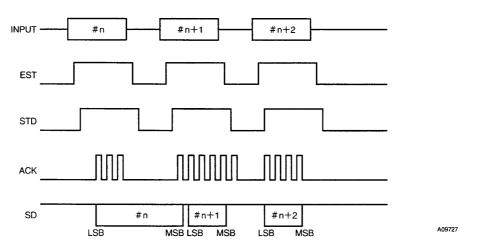

### **Timing Chart**

Normal State Timing Chart

When the DTMF signal (#n) is split due to, for example, the burst signal

When noise (#n+a) similar to a DTMF signal is input

Data is output from the SD pin after 4 pulses are input to the ACK pin. However, note that if 5 or more pulses are input between one rising edge on the EST pin and the next rising edge on the EST pin, the fifth and later pulses will be ignored.

#### **ACK/SD Timing Chart**

Reset Timing at Power On

#### **Filter Characteristics**

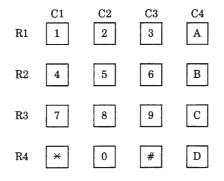

#### **Output Code Table**

| FL  | F <sub>H</sub> | Key | b3 | b2 | b1 | b0 |

|-----|----------------|-----|----|----|----|----|

| 697 | 1209           | 1   | L  | L  | L  | Н  |

| 697 | 1336           | 2   | L  | L  | Н  | L  |

| 697 | 1477           | 3   | L  | L  | Н  | Н  |

| 770 | 1209           | 4   | L  | Н  | L  | L  |

| 770 | 1336           | 5   | L  | Н  | L  | Н  |

| 770 | 1477           | 6   | L  | Н  | Н  | L  |

| 852 | 1209           | 7   | L  | Н  | Н  | Н  |

| 852 | 1336           | 8   | Н  | L  | L  | L  |

| 852 | 1477           | 9   | Н  | L  | L  | Н  |

| 941 | 1336           | 0   | Н  | L  | Н  | L  |

| 941 | 1209           | *   | Н  | L  | Н  | Н  |

| 941 | 1477           | #   | Н  | Н  | L  | L  |

| 697 | 1633           | A   | Н  | Н  | L  | Н  |

| 770 | 1633           | В   | Н  | Н  | Н  | L  |

| 852 | 1633           | С   | Н  | Н  | Н  | Н  |

| 941 | 1633           | D   | L  | L  | L  | L  |

#### **DTMF Dialing Matrix**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 1998. Specifications and information herein are subject to change without notice.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.